Differentiate your RISC-V SoC with MIPS eVocore CPUs

Coherent Multi-Thread, Multi-Core, Multi-cluster Scalability

MIPS & RISC-V: Powering Autonomous Driving with eVocore CPUs

MIPS' VP, Itai Yarom, and RISC-V CEO, Calista Redmond, discuss cutting-edge RISC-V CPUs, collaborative efforts, and Mobileye's integration of AI accelerators with MIPS eVocore for autonomous driving.

"The new MIPS eVocore CPUs provide not only the unrivaled combination of performance and efficiency that MIPS is known for, but also the differentiation of an open software development environment.”

“With MIPS’ strategic shift to RISC-V, we are pleased to continue our long-standing relationship with new technology and innovation for verification for the latest MIPS RISC-V based Applications-Class processors.”

“We are excited to see MIPS, one of the first companies to bring a RISC based architecture to the market back in the 1980s, now expanding to offer RISC-V ISA compliant cores. We’ve a long history of working together.”

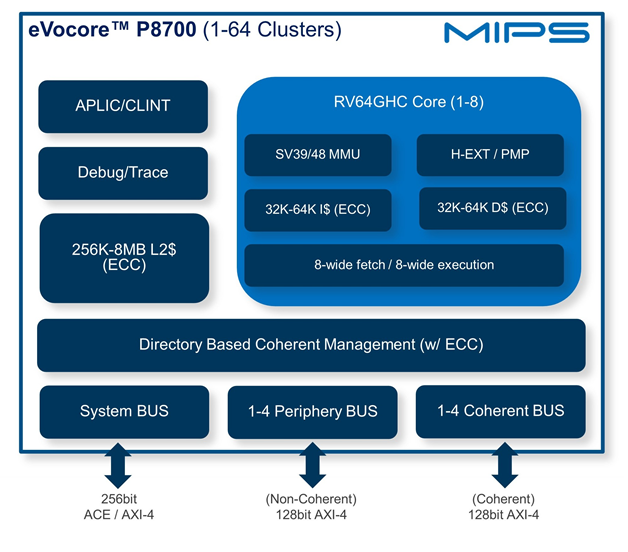

MIPS eVocore P8700

Experience exceptional processing capabilities with the eVocore P8700. This cutting-edge system synergizes an advanced pipeline with multi-issue Out-of-Order (OoO) execution and multi-threading to produce remarkable computational throughput. Boasting single-threaded performance that surpasses existing RISC-V CPU IP options, the P8700 has the ability to expand up to 64 clusters, 512 cores, and 1,024 harts/threads for unparalleled scalability and power.

AWARD WINNER

MIPS Takes Top Honors at Embedded World for eVocore P8700 Multiprocessor

Company's First RISC-V Product Paves Way for Future of Chip Development

RISC-V CPUs for the New Era of Heterogeneous Computing

Srinivas Kantheti, MIPS

A Peek Inside a New RISC-V CPU for Autonomous Vehicles

Itai Yarom, MIPS

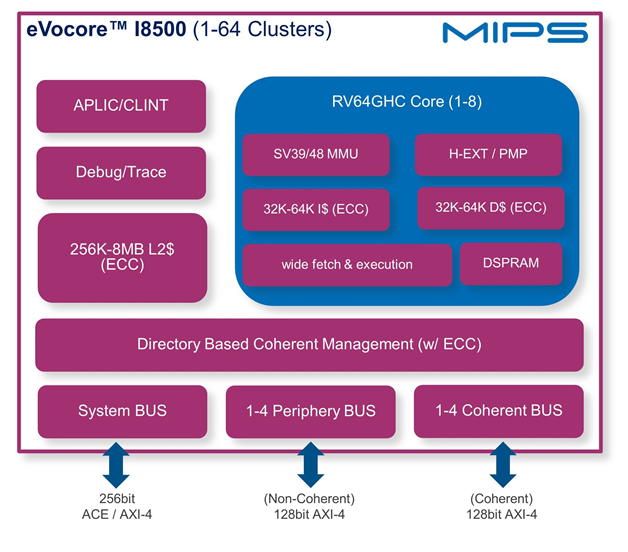

MIPS eVocore I8500

The eVocore I8500 sets the standard for power-efficient in-order multiprocessing systems, designed specifically for SoC applications. Each I8500 core expertly fuses multi-threading with a highly efficient triple-issue pipeline, ensuring remarkable computational throughput. This versatile solution has the capacity to expand up to 64 clusters, 512 cores, and 2,048 harts/threads, making it a top choice for performance and scalability.

MIPS Partners With Mobileye to Accelerate Next Generation Autonomous Driving Technologies and Advanced Driver Assistance Systems

Mobileye Adopts New MIPS eVocore RISC-V CPUs; RISC-V Architecture to Help Drive Future of Vehicle Safety